簡單認識芯片里的電阻電容

我們熟悉的電阻、電容,在集成電路里是什么樣的?一起來初步學習集成電路版圖設計中的電阻和電容知識,做一次芯片級的秘境探幽。

1. 電阻

1.1 薄膜電阻與方塊電阻

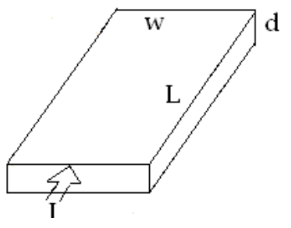

集成電路的電阻一般由擴散或者淀積層形成,通常可以用厚度一定的薄膜作為模型。選個矩形的薄膜,我們就有了這樣的一個方塊電阻。

材料決定了這個電阻的電阻率為ρ,矩形薄膜的長度為L,寬度W,厚度d,

其電阻值應為 R=ρL/Wd.

做版圖設計時ρ和d是定量,我們取長寬各為1,就有了一個方塊電阻Rs,于是設計中只要自己控制長度與寬度,就有了不同阻值的電阻R,計算公式為:

R=Rs*L/W(Rs單位為歐姆/sq)

那么版圖中只要給出長和寬,就得到需要的電阻?且慢,電阻的阻值不能由這個公式簡單計算,必須考慮工藝因素和電流特點這些附加因素。

1.2 附加因素的電阻版圖

光刻的過程會引起氧化層窗口輕微的擴張或收縮,橫向的擴散會導致電阻變寬,接觸孔附近電流的不均勻也會影響阻值,這些需要在版圖設計中做調整,才能得到需要的阻值。

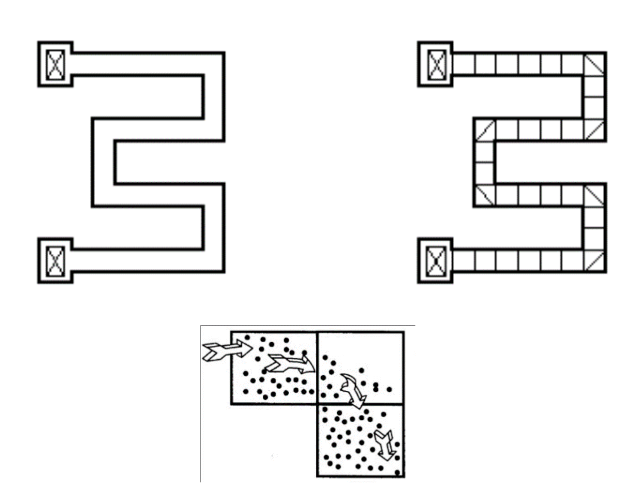

版面上布圖,圖形有拐角是正常的,但電流并不均勻地流過電阻的拐角處,拐角處的方塊電阻約為0.56sq;版圖的拐角要用調整的公式計算。

電阻版圖示例

這里應用了拐角式電阻而非普通電阻的原因:

1)普通電阻L/W不能小于2/1;

2)普通電阻存在連接點,所以電阻值并非平均分布。

1.3 電阻溫度系數

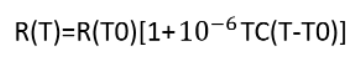

溫度的影響在集成電路版圖設計中必須考慮,電阻的阻值受溫度的影響,電阻溫度系數公式為:

R(T)為溫度T下的電阻,R(T0)為溫度T0下的阻值,TC是以百萬分之一每攝氏度為單位的電阻溫度系數(TRC)。

2. 電容

用到電容的時候,電容C的邏輯定義是這樣的:

Q=CV

其中Q代表施加在導體上的電荷,V代表電荷引起的電勢差,C就是通常所稱的電容。C其實是電容的比例常數,其數值是由電容的幾何和物理參數(極板面積,板間距,極板間電解質參數等等)決定。

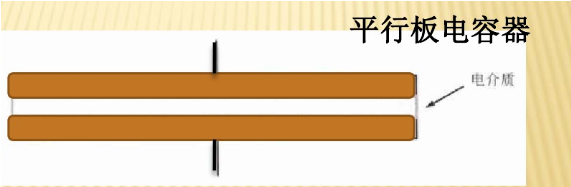

集成電路中所有的電容都是平行板電容器(parallel-plate capacitor),它由被稱為電極的兩塊導電平板和一層被稱為電介質的絕緣材料構成。

2.1 常見電容的原理及版圖

2.1.1. MIM電容

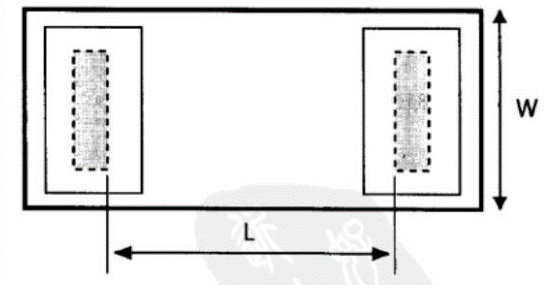

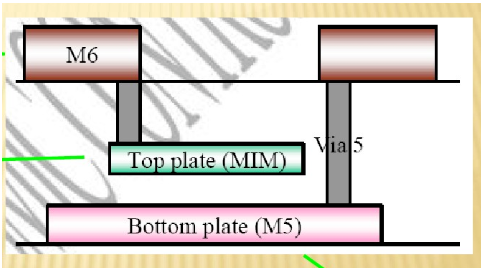

集成電路中最常見的電容,通常由頂層金屬Mn以及下一層金屬Mn-1構成,因金屬層間存在氧化層距離較遠,所以電容值不大。為解決此問題一般會在兩層金屬間引入一層光罩,再用孔(VIA)將上極板與之相連,所以MIM電容實際上是光罩與下極板之間的電容,此時極板間距離縮短,電容值變大。

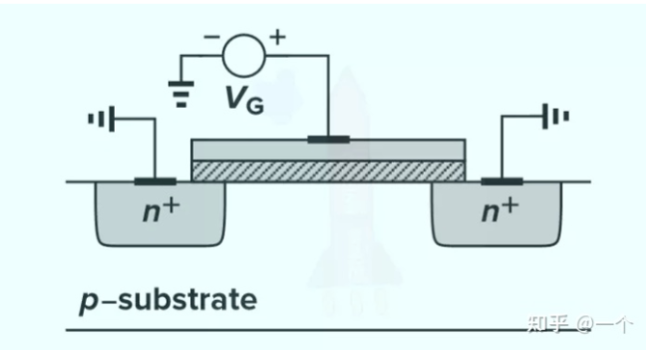

2.1.2. MOS電容

如圖所示,我們將MOS管的源,漏,襯底和地相連,此時當柵極電壓大于閾值電壓時,在源漏間便形成溝道,此時柵極----柵氧化層----溝道這樣一個電容便形成了。

優點:節省面積,MOS電容可以和MIM電容、MOM電容同時存在,將面積的利用率提高。

缺點:當柵極電壓變化時,MOS電容的大小也會同時改變,所以MOS無法使用在高精度電路中,模擬電路的前端采樣更是不可能露面。

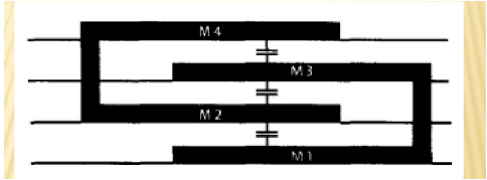

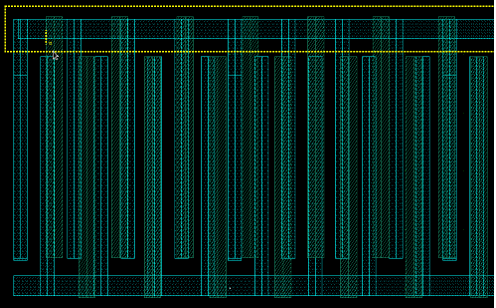

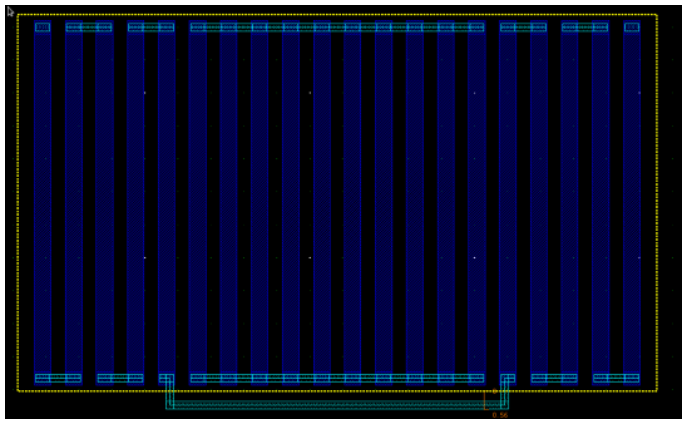

2.1.3. MOM電容

利用底層金屬M1,M2制作的插指電容,即同層metal邊沿之間的寄生電容。

優點:節省面積

缺點:電容值確定性和穩定性不好

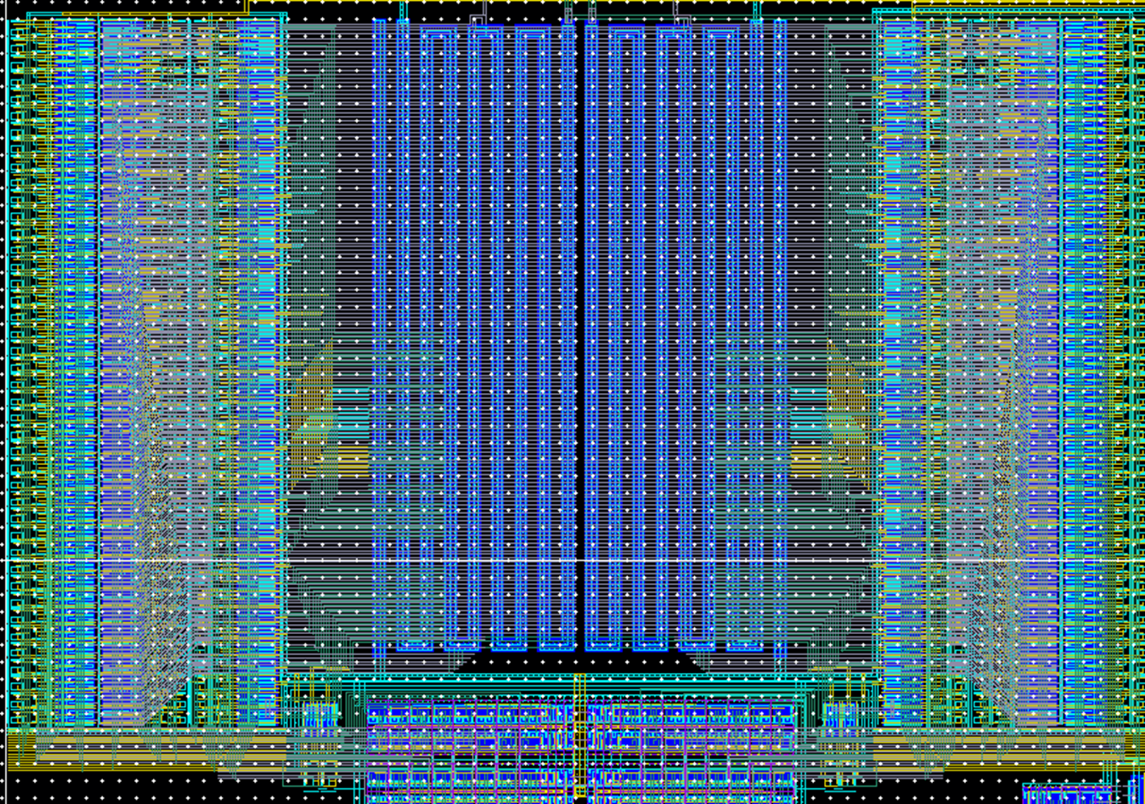

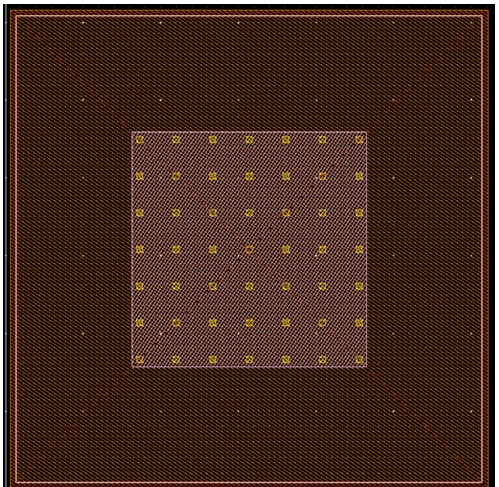

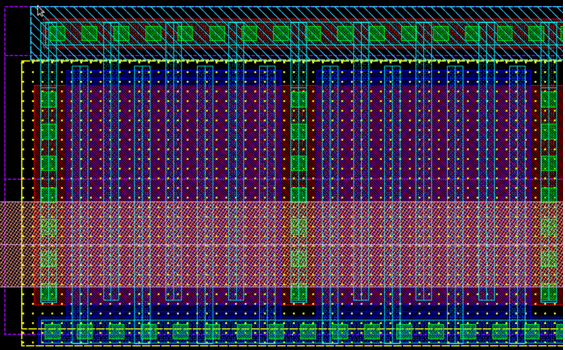

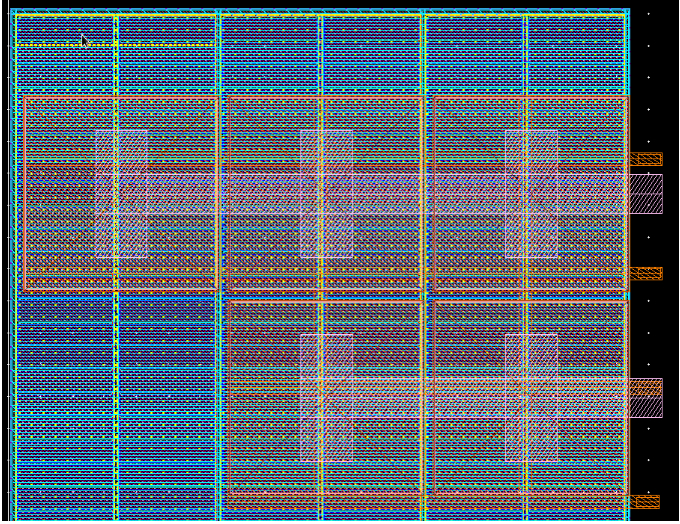

三種電容同時存在的版圖

3. 電阻與電容的失配問題

3.1 失配的原因----隨機變化

所有器件在尺寸和構成上都存在微觀的不規則性,于是設計與實際的結果會有偏差。對于一對器件,我們會設計需要的匹配程度。

比如一對10kΩ的電阻,制作后測得電阻為12.47kΩ和12.34kΩ。兩實際電阻的比例為1.0105,與預期相差1%,即這對電阻表現出1%的失配。

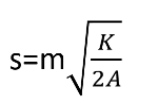

常用的失配參數:

S表示面積為A器件的標準差,m表示面積為A器件的平均值,k叫做匹配系數,這個系數取決于失配源。

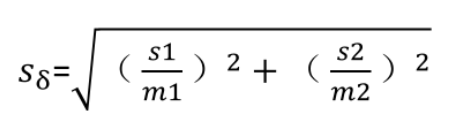

公式中的m1和m2是每個器件研究參數的平均值,S1和S2是該參數標準差。

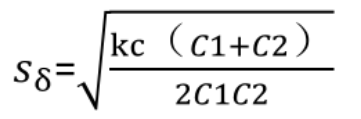

3.2 電容

任意兩個電容C1,C2間的失配為

由此式可以看出當C1=C2時,可以使該式值最小,所以為了減小失配,應該避免使用大比例的匹配電容。

課后習題

如何繪制一組阻值為1:100的匹配電阻,可以使得失配盡量小?

答案:

北京久好電子科技有限公司

致力于數模混合集成電路的設計,旗下各種壓力、溫濕度傳感器信號調理芯片獲得市場的廣泛認可。產品具備高穩定性、高可靠性、高性價比,助力客戶實現成功。